Oracle’s database and high-performance workloads will run faster with the company’s latest SPARC M6 chip, which has been tuned specially for the Oracle applications.

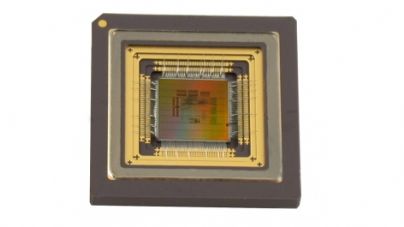

The latest SPARC processor has 12 processor cores, effectively doubling the number of cores than its predecessor, M5, which shipped earlier this year. Each M6 core will be able to run eight threads simultaneously, giving the chip the ability to run 96 threads simultaneously, said Ali Vahidsafa, senior hardware engineer at Oracle, during a presentation about M6 at the Hot Chips conference in Stanford, California.

SPARC has been around for more than two decades, and the goal with M6 is to push the processor deeper into high-performance and highly parallel systems, Vahidsafa said, adding that the new chip will help expand Oracle’s portfolio of high-end servers.

"What runs on these servers is consolidation of virtual workloads, and single-image databases, in particular in-memory databases and application. Both of those can benefit from higher thread count and higher memory footprint," Vahidsafa said.

It is also imperative that the benefits of the new chip be accessible to current workloads and software, Vahidsafa said.

Multithreaded applications will benefit most from the new chip, but single-threaded applications will have access to the specific "Critical Thread" queue thanks to a feature in OS scheduling, which could speed up workloads.

Some other chip features have not changed from the M5, which was the first high-end enterprise SPARC chip variant with a higher cache-to-core ratio. The M6 chip will have 48MB of L3 cache, and support 1TB of memory per socket. Oracle did not reveal the clock speed of the chip.

The chip has been tuned for in-memory databases and applications with four DDR3 schedulers to better organise traffic and visibility of tasks, Vahidsafa said. The memory subsystem has been organised for system designers to balance performance, power and serviceability.

The processors also can be linked to create two-way, four-way or eight-way servers. Using special boxes called Bixby, the chip will also allow for creation of 32-way, 48-way or even 96-way servers, with memory and other resources being shared. The M6 has features to balance out performance in servers to reduce latency and to ensure transactions are quickly processed. The coherency features have been built from the ground up for larger systems, and can be applied to smaller server pools, Vahidsafa said.

The chip also has new reliability, availability and serviceability (RAS) features to track down errors in the system, which ensures high server uptime. In conjunction with the Solaris OS, a three-step process identifies errant threads, cores or cache, which are isolated, reported and then cleaned up. It also has ECC memory.

Vahidsafa declined to comment on when the chip would become available in servers.

Another SPARC chip got attention at Hot Chips, with Fujitsu sharing details about its latest mainframe chip called SPARC X+. The 16-core chip runs at 3.5GHz and higher, and can be used in mainframes with up to 64 sockets. Each core will support two simultaneous threads, with the ability for a mainframe to run 2,048 threads simultaneously. On-chip software helps accelerate database applications, said Toshio Yoshida , director in the processor development division at Fujitsu.

IDG News Service

Subscribers 0

Fans 0

Followers 0

Followers